GL854G is Genesys Logic’s premium 7-port hub solution which fully complies with Universal Serial Bus Specification Revision 2.0. GL854G implements multiple TT* (Note1) architecture that provide dedicated TT* to each downstream (DS) ports, which guarantee Full-Speed(FS) data passing bandwidth when multiple FS device perform heavy loading operations. The controller inherits Genesys Logic’s cutting edge technology on cost and power efficient serial interface design. GL854G has proven compatibility, lower power consumption figure and better cost structure above all USB 2.0 hub solutions worldwide.

GL854G implements multiple hub configuration features onto internal mask ROM, which traditionally requires external EEPROM. The microprocessor detects general purpose I/O (GPIO) status during the initial stage to configure hub settings such as (1) declare of compound device (2) gang/individual mode selection…etc. External EEPROM can be removed if no vendor specified PID/VID or product string is required for the application.

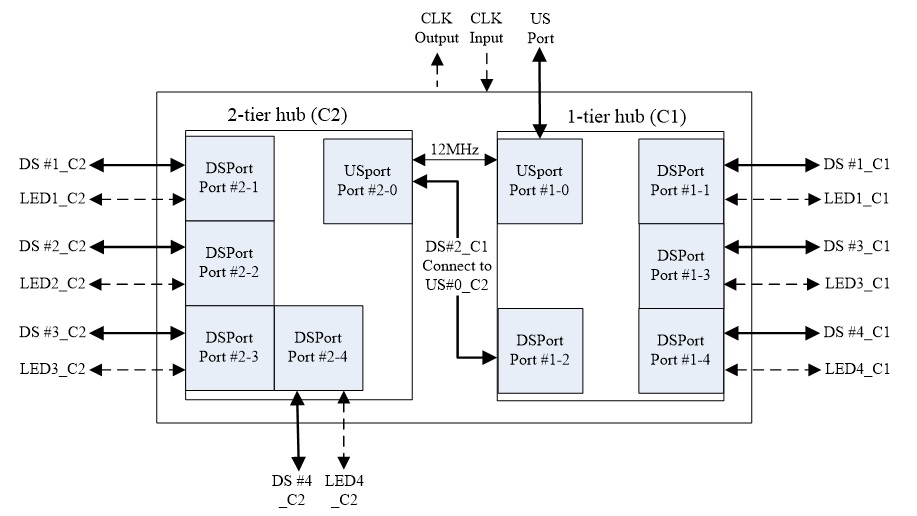

GL854G provides 12MHz clock output that can be used as a reference clock source for multi-chip, hub compound applications. The output clock provides enough driving capacity to support up to 2 devices that connected to the downstream port. The chip-to-chip clock trace is relatively sensitive to PCB noise. Please refer to design guide for PCB layout suggestions.

*Note 1: TT (transaction translator) is the main traffic control engine in an USB 2.0 hub to handle the unbalanced traffic speed between the upstream port and the downstream ports.

- Multiple Chip Package (MCP) architecture

- Integrates two standard USB 4-port hub silicon dies into single chip

- Supports 7 USB 2.0 compliant downstream ports

- Multiple Transaction Translator (MTT)

- Provides dedicated TT control logics for each downstream port

- Superior performance when multiple FS devices operate concurrently

- Compliant with USB specification Revision 2.0

- Upstream port supports both high-speed (HS) and full-speed (FS) traffic

- Downstream ports support HS, FS, and low-speed (LS) traffic

- Backward compatible to USB specification Revision 1.1

- Each downstream port supports status indicator, with automatic and manual modes

- Conform to self power and bus power requirements

- Integrated USB transceiver

- Compliant with USB electrical requirements

- Ultralow power consumption

- Improve output drivers with slew-rate control for EMI reduction

- Internal power-fail detection for ESD recovery

- On-chip 8-bit micro-processor

- Support customized PID, VID by reading external EEPROM

- Support downstream port configuration by reading external EEPROM

- Smart power management features

- Support individual / gang mode over-current detection for all downstream ports

- Automatic switching between self-powered and bus-powered modes

- Lower BOM cost

- Single external 12 MHz crystal / Oscillator clock input

- On-chip 5V to 3.3V power regulator

- Built-in upstream port 1.5KΩ pull-up and downstream port 15KΩ pull-down resistors

- Support low-cost 24C02 EEPROM

- Features for hub compound applications

- Support compound-device (non-removable in downstream ports) by I/O pin configuration

- Provide 12MHz clock source for other USB device connected to the downstream ports

- Available package type: 64 pin LQFP package (7x7mm)

- Applications:

- UMPC/MID, motherboard on-board applications

- Consumer electronics built-in hub application

- Monitor built-in hub

- Embedded systems

- Hub compound applications